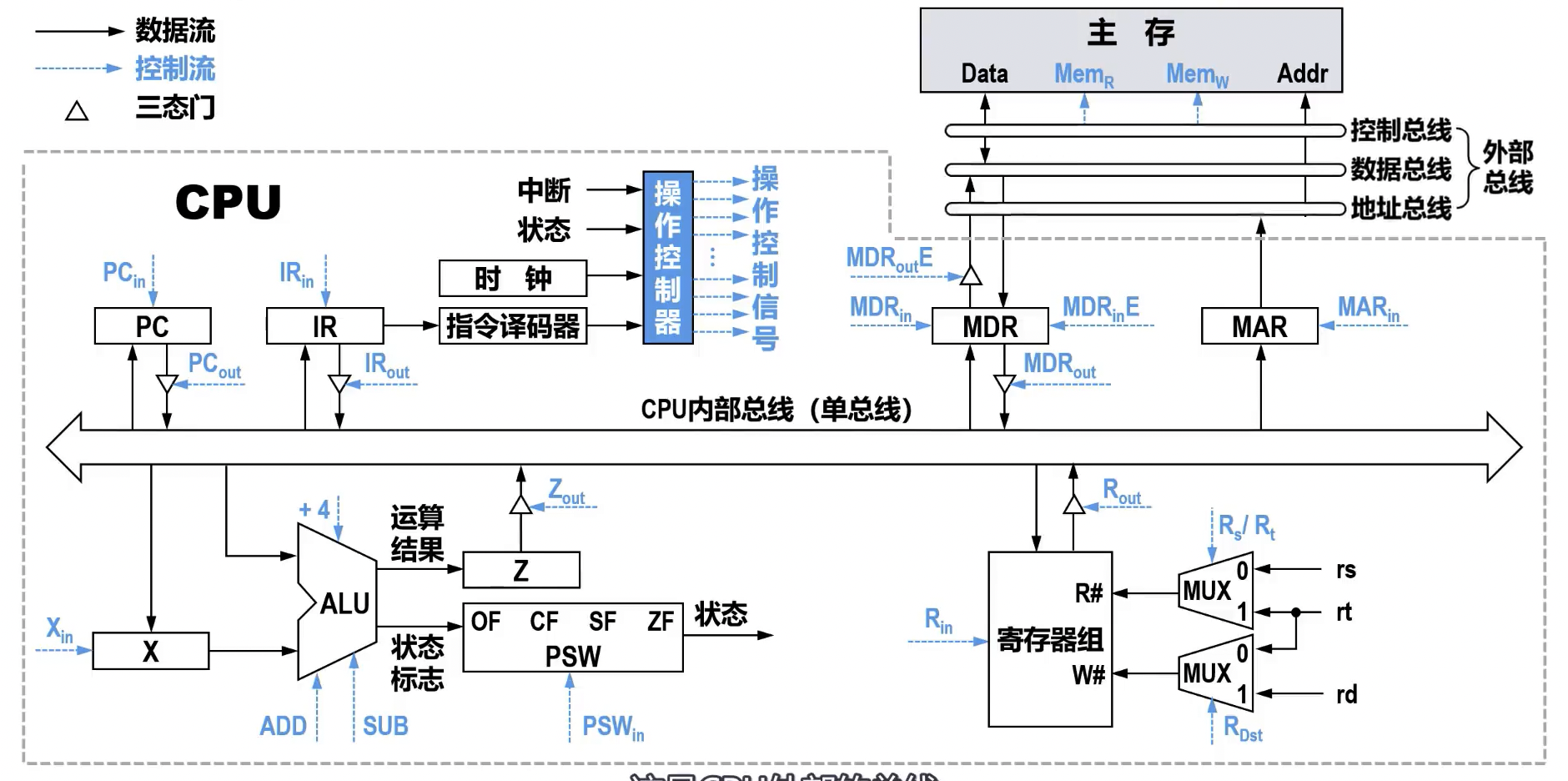

数据通路的功能和基本结构

数据通路概述

- 定义:

- 数据在指令执行的过程中所经过的路径,包括路径上的部件,称为数据通路

- ALU、通用寄存器、状态寄存器、异常和中断处理逻辑等都收数据通路的一部分

- 它描述了信息从哪里开始,中间经过哪些部件,最后被传送到哪里

- 功能:实现 CPU 内部的运算器与寄存器及寄存器之间的数据交换

- 易混淆知识点:

- 数据通路是由控制部件控制,控制部件根据每条指令功能的不同生成对数据通路的控制信号

- 单总线数据通路将所有寄存器的输入输出端都连接在一条公共通路上,一个时钟内只允许一次操作,无法完成指令的所有操作

- CPU 的读 / 写控制信号线决定了是从存储器读还是向存储器写

- 内部总线是指同一部件之间的线,系统总线是同一台计算机系统各部件之间的线

数据通路的基本结构

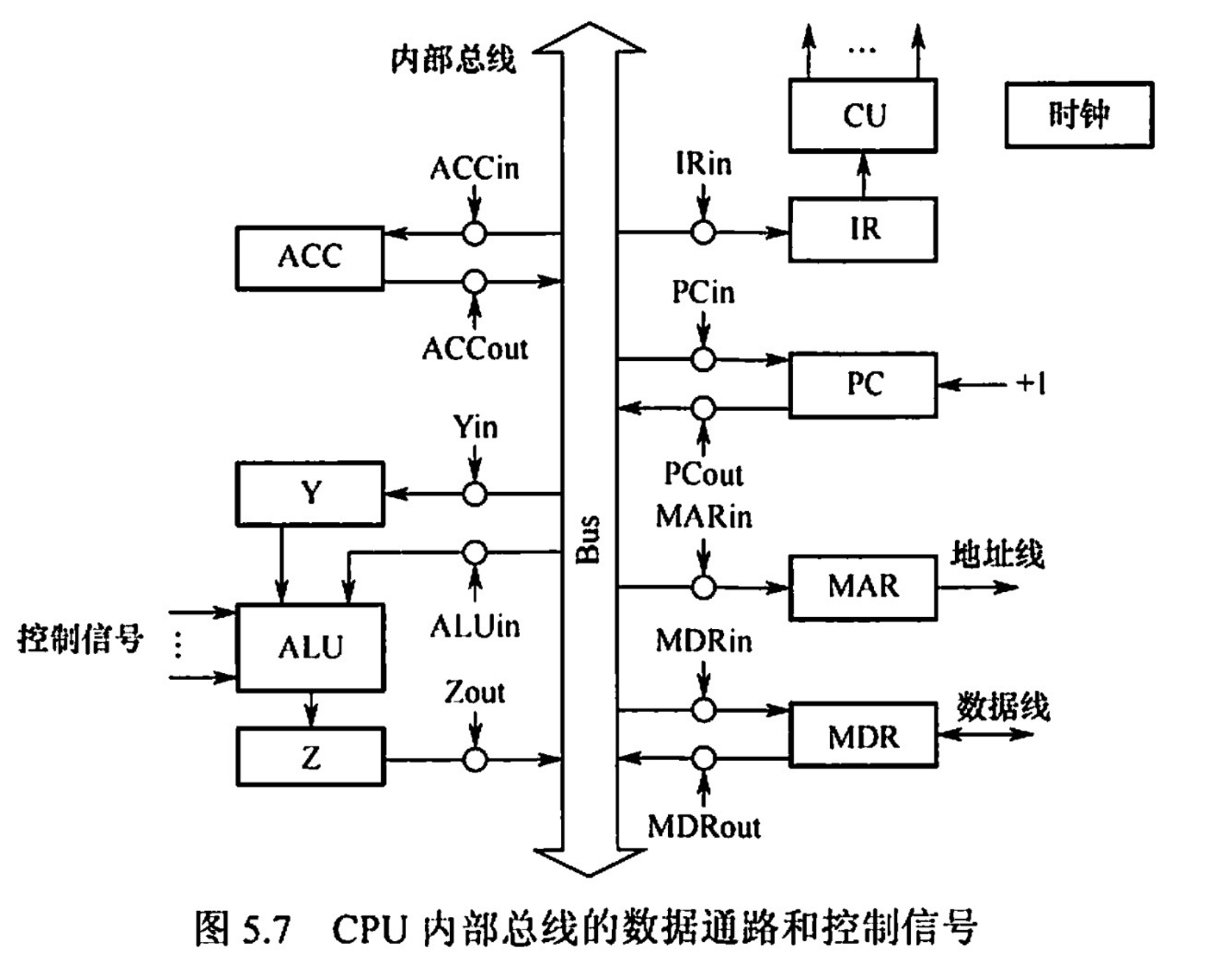

CPU 内部单总线方式

- 定义:将所用寄存器的输入端与输出端连接到一条公共通路上

- 特点:结构比较简单,数据传输存在较多的冲突现象,性能较低

- in 表示该部件的允许输入控制信号;out 表示该部件的允许输出控制信号

- ALU 只能有一个输入端与总线相连,另一个输入端需要通过暂存器与总线相连

CPU 内部多总线方式

- 定义:将所用寄存器的输入端与输出端都连接到多条公共通路上

- 特点:相较单总线结构,效率较高

专用数据通路方式

- 定义:根据指令执行过程中的数据和地址的流动方向安排连接线路

- 特点:避免使用共享的总线,性能较好,但硬件总量较大

数据通路的操作举例

以 CPU 内部单总线数据通路为例:

通用寄存器直接传送数据

以程序计数器 PC 为例:

将 PC 的内容传送至 MAR,实现该操作的流程及控制信号为

T1: (PC)->MAR # PCout 和 MARin 有效,PC 内容 -> MAR数据通路的操作举例

以 CPU 内部单总线数据通路为例:

通用寄存器直接传送数据

以程序计数器 PC 为例:

将 PC 的内容传送至 MAR,实现该操作的流程及控制信号为

(PC)->MAR # PCout 和 MARin 有效,PC 内容 -> MAR操作说明:此操作通过内部总线完成,无需 ALU 参与,一个时钟周期内完成。

从主存读取数据

以 CPU 从主存中取指令为例:

T1: (PC)->MAR # PCout 和 MARin 有效,PC 内容送入 MAR

T2: (MAR)->地址总线 # MARout 有效,地址送至主存

发出读命令 # MemRead 有效,启动内存读操作

T3: 数据总线->MDR # 等待主存响应,数据返回到 MDR

(MDR)->IR # MDRout 和 IRin 有效,指令送入指令寄存器操作说明:取指操作需要多个时钟周期,包括地址传送、内存访问和数据接收。

将数据写入主存

将寄存器 R1 的内容写入寄存器 R2 所指的内存单元,实现该操作的流程及控制信号为:

T1: (R2)->MAR # R2out 和 MARin 有效,R2 内容作为地址送入 MAR

T2: (R1)->MDR # R1out 和 MDRin 有效,R1 内容送入 MDR

T3: (MAR)->地址总线 # MARout 有效,地址送至主存

(MDR)->数据总线 # MDRout 有效,数据送至主存

发出写命令 # MemWrite 有效,启动内存写操作操作说明:写内存需要准备地址和数据,通过地址总线和数据总线完成数据传送。

执行算数或逻辑运算

以执行加法运算 R3 = R1 + R2 为例:

T1: (R1)->Y # R1out 和 Yin 有效,操作数1送入Y寄存器

T2: (R2)->ALU输入B # R2out 有效,操作数2送入ALU的B端

Y->ALU输入A # Yout 有效,Y寄存器内容送入ALU的A端

ALU执行ADD操作 # ALU控制信号设为ADD

T3: (ALU输出)->Z # ALU运算结果送入Z寄存器

T4: (Z)->R3 # Zout 和 R3in 有效,结果送入R3操作说明:算术运算需要通过 ALU 完成,使用 Y 寄存器暂存一个操作数,Z 寄存器暂存运算结果。

修改程序计数器的值

顺序执行(PC 自增):

T1: (PC)->Y # PCout 和 Yin 有效,当前PC值送入Y寄存器

T2: 4->ALU输入B # 常数4送入ALU(假设指令长度为4字节)

Y->ALU输入A # Yout 有效,PC值送入ALU

ALU执行ADD操作 # ALU控制信号设为ADD,计算PC+4

T3: (ALU输出)->Z # 运算结果送入Z寄存器

T4: (Z)->PC # Zout 和 PCin 有效,更新PC值跳转指令执行:

(条件跳转)

T1: 检查条件码 # 根据标志位判断是否跳转

T2: (IR地址字段)->PC # 如果条件满足,IRout 和 PCin 有效,跳转地址送入PC

或 执行PC+4 # 如果条件不满足,执行顺序地址递增操作说明:PC 修改包括顺序执行时的自增和跳转指令时的地址更新,是指令执行流程控制的关键环节。