CPU 的功能和基本结构

CPU 的功能

与 CPU 的结构密切相关

- 指令控制:

- 完成取指令、分析指令和执行指令的操作,即程序的顺序控制

- 操作控制:

- 管理并产生由内存取出的每条指令的操作信号

- 把各种操作信号送往相应的部件,从而控制这些部件按指令的要求进行动作

- 时间控制:

- 严格控制各种操作信号的出现时间、持续时间及出现的时间顺序

- 数据加工:

- 对数据进行算术和逻辑运算

- 中断处理:

- 对计算机运行过程中出现的异常情况和特殊请求进行处理

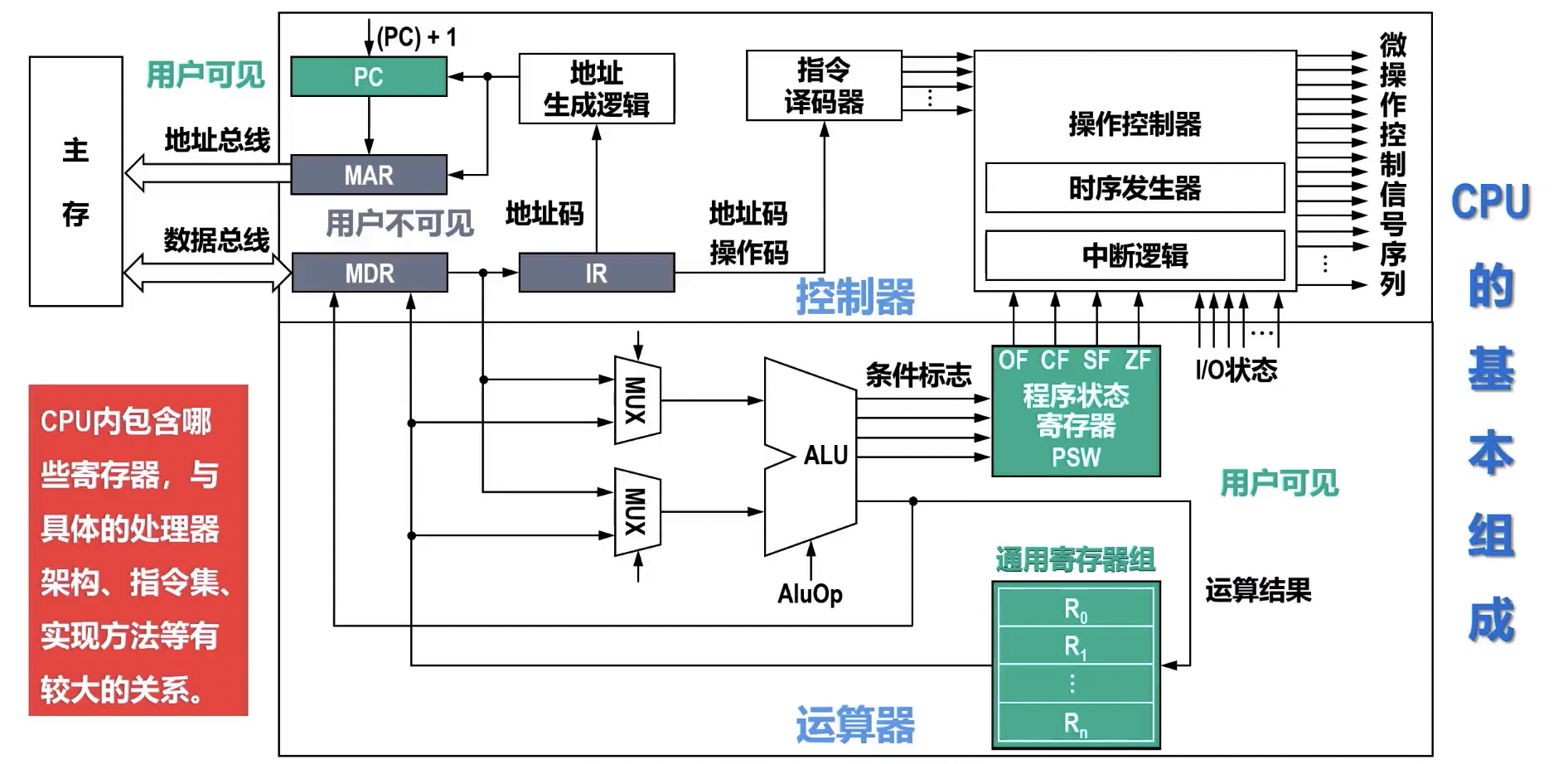

CPU 的基本结构

组成部分

- CPU = 运算器 + 控制器

- 运算器:对数据进行加工

- 控制器:负责协调并控制计算机各部件执行程序的指令

- CPU = 数据通路 + 控制部件

CPU 寄存器的分类

按汇编语言(或机器语言)程序是否可以访问

用户可见的寄存器

- 可对这类寄存器编程,程序员可以通过指令直接访问和操作。

- 使用这类寄存器可减少对主存储器的访问次数,提高 CPU 执行速度。

- 如:

- 通用寄存器 (General Purpose Registers):存放操作数或地址,可作为累加器、变址寄存器、基址寄存器等多种用途。

- 程序计数器 (Program Counter, PC):存放下一条待执行指令的地址,CPU 依据 PC 内容取指令。

- 程序状态字寄存器 (Program Status Word, PSW):存放程序运行状态信息和条件码,如标志位(零标志 ZF、符号标志 SF、溢出标志 OF、进位标志 CF 等)以及中断允许标志、特权级等控制信息。

- 累加寄存器 (Accumulator, AC):专门用于存放算术逻辑运算的一个操作数和运算结果。

- 变址寄存器 (Index Register, IX):存放变址量,用于形成操作数的有效地址,实现变址寻址。

- 基址寄存器 (Base Register, BR):存放基地址,用于形成操作数的有效地址,实现基址寻址。

- 栈指针寄存器 (Stack Pointer, SP):存放栈顶地址,用于管理栈操作(压栈和弹栈)。

用户不可见的寄存器

- 对用户透明,不可编程,程序员不能通过指令直接访问。

- 被控制部件使用,以控制 CPU 的操作,协调各部件工作,如指令的取指、译码、执行等阶段。

- 如:

- 存储器地址寄存器 (Memory Address Register, MAR):存放要访问的存储单元的地址,其内容直接送往地址总线。

- 存储器数据寄存器 (Memory Data Register, MDR):存放从存储器读取的数据或要写入存储器的数据,其内容直接与数据总线连接。

- 指令寄存器 (Instruction Register, IR):存放当前正在执行的指令,其内容送往指令译码器。

- 暂存寄存器 (Temporary Register, TMP/DR):临时存放操作数或中间结果,供 ALU 使用,或用于数据周转。

运算器基本结构

功能

- 运算器是计算机对数据进行加工处理的中心,执行所有的算术运算(如加、减、乘、除)和逻辑运算(如与、或、非、异或)。

- 接收从控制器送来的命令并执行相应的动作,对数据进行加工和处理,并将运算结果送回或存入指定位置。

基本组成部件

- 算术逻辑单元(ALU): 运算器的核心部件,负责执行各种算术运算(如加、减、乘、除)和逻辑运算(如与、或、非、异或)。它是对数据进行加工处理的逻辑电路。

- 程序状态字寄存器(PSW):

- PSW 存放程序状态字【标志位的组合】,用于保存系统的运行状态和运算结果的特征。

- PSW 包括:

- 状态标志:反映运算结果的特征,如溢出标志 (OF)、符号标志 (SF)、零标志 (ZF)、进位标志 (CF) 等。

- 控制标志:控制指令的执行或 CPU 的工作状态,如中断标志、陷阱标志等。

- 累加寄存器(ACC): 是一个特殊的通用寄存器,主要用于暂存 ALU 运算的结果信息,并可作为加法运算的一个输入端,方便连续运算。

- 通用寄存器组(GPRS):

- 用于存放操作数和各种地址信息,如 x86 架构中的 AX, BX, CX, DX 等。

- 其位数通常与机器字长相等。

- 部分通用寄存器具有特殊用途,例如 SP (堆栈指针) 用于指示栈顶地址。

- 暂存寄存器: 暂存从数据总线或通用寄存器读来的操作数,通常对应用程序员透明,用于 ALU 内部运算的临时存储。

- 移位寄存器(SR): 用于对操作数或运算结果进行移位运算(如逻辑移位、算术移位、循环移位),常用于实现乘除法运算的辅助操作。

- 计数器: 用于控制乘除运算等复杂操作的步数,确保运算过程的正确执行。

控制器基本结构

功能

- 协调并控制计算机各部件执行程序的指令序列

- 基本功能包括取指令、分析指令、执行指令

- 取指令:自动形成指令地址;自动发出取指令的命令

- 分析指令:操作码译码(分析本条指令要完成什么操作),产生操作数的有效地址

- 执行指令:根据分析指令得到的“操作命令”和“操作数地址”,形成操作信号控制序列,控制运算器、存储器以及 I/O 设备完成相应的操作

- 中断处理:管理总线及输入输出;处理异常情况(如掉电)和特殊请求(如打印机请求打印一行字符)

组成

- 程序计数器(PC):

- 用于指出下一条指令在主存中的存放地址(PC 总是存放指令地址)

- PC 有自增功能

- PC 的值会根据 CPU 在执行指令过程中自增或转移到程序的某处 (跳转指令)

- PC 的位数等于主存储器地址位数

- 指令寄存器(IR):

- 用于保存当前正在执行的那条指令

- IR 的位数取决于指令字长

- 指令译码器(ID):

- 仅对操作码字段进行译码,以确定指令的操作功能

- 存储器地址寄存器(MAR):

- 存放要访问的主存储器单元的地址

- MAR 的位数等于主存储器地址线位数

- 存储器数据寄存器(MDR):

- 存放向主存储器写入的信息或从主存储器读出的信息

- MDR 的位数等于存储字长

- 时序系统:用于产生各种时序信号,都由统一时钟 CLOCK 分频得到

- 微操作信号发生器:

- 根据 IR 的内容 (指令),PSW 的内容 (状态信息) 和时序信号产生控制计算机系统所需的各种控制信号

- 有组合逻辑型和存储逻辑型

数据通路基本结构

专用数据通路方式

- 根据指令执行过程中的数据和地址的流动方向安排连线线路

- 使用多路选择器控制一路的输出

- 使用三态门控制输出

- 优点:性能较高,基本不存在数据冲突现象

- 缺点:结构复杂,硬件量大,不易实现

CPU 内部单总线方式

- 将所有寄存器的输入端和控制端都连接到一条公共通路

- 优点:结构简单,容易实现

- 缺点:传输存在较多冲突现象,性能较低

CPU 常混淆点

- 转移指令时,需要判别转移是否成功,若成功则 PC 修改为转移指令的目标地址,否则下一条指令的地址仍然为 PC 自增后的地址

- 计算机分两大部分:控制部件和执行部件

- 控制器就是控制部件,指令寄存器,操作控制器,程序计数器都是控制部件

- 运算器,存储器,外围设备就是执行部件

- 各寄存器的位数等于什么?【和地址有关的就取决于机器字长,和数据大小有关的就取决于容量】

- 通用寄存器:机器字长

- PC:

- 按字节编址:与存储器地址的位数相等,取决于存储器容量

- 按字编址:位数 = 存储器地址的位数 - 【指令必须按边界对齐的方式存放】,取决于存储器容量和存储字长

- IR:指令字长

- MAR:存储器容量

- MDR:存储字长